Technische Universität Chemnitz Straße der Nationen 62 09111 Chemnitz

# FPGA-basierte Fail-safe-Schnittstellen für eingebettete Systeme

## Studienarbeit

Fakultät für Informatik Studiengang Informatik Professur Technische Informatik Vertiefungsrichtung Eingebettete Systeme

> von Marcel Flade Dorfstraße 81 09526 Pfaffroda-Hallbach

Betreuer: Dipl. Inf. Stefan Ihmor, Universität Paderborn Prüfer: Prof. Dr. habil. Wolfram Hardt, TU Chemnitz

im November 2003

# Inhaltsverzeichnis

| 1 |     | führun  |                                                               |

|---|-----|---------|---------------------------------------------------------------|

|   | 1.1 |         | benstellung                                                   |

|   | 1.2 | Gliede  | rung der Arbeit                                               |

| 2 | Gru | ındlage | en 3                                                          |

|   | 2.1 | Das M   | Iodell des Interfaceblock (IFB)                               |

|   |     | 2.1.1   | Die Kontrolleinheit (CU)                                      |

|   |     | 2.1.2   | Die Protokollhandler (PH)                                     |

|   |     | 2.1.3   | Der Sequenzhandler (SH) 6                                     |

|   |     | 2.1.4   | Der Modus                                                     |

|   | 2.2 | Definit | tion des Protokollbegriffs                                    |

|   | 2.3 | FPGA    |                                                               |

|   |     | 2.3.1   | Konfigurierbare Logikblöcke                                   |

|   |     | 2.3.2   | IO-Blöcke                                                     |

|   |     | 2.3.3   | Verbindungsstruktur                                           |

|   |     |         |                                                               |

| 3 |     |         | Verhalten 15                                                  |

|   | 3.1 |         | lnung und Bedeutung                                           |

|   | 3.2 |         | von Fehlern bei Schnittstellen                                |

|   | 3.3 | _       | chkeiten der Fehlererkennung                                  |

|   |     | 3.3.1   | -                                                             |

|   |     | 3.3.2   | Rechteckcode                                                  |

|   |     | 3.3.3   | Hammingcodes                                                  |

|   |     | 3.3.4   | Zyklische Codes (CRC)                                         |

|   |     | 3.3.5   | Frame-Check                                                   |

|   |     | 3.3.6   | ACK-Fehler Erkennung                                          |

|   |     | 3.3.7   | Monitoring                                                    |

|   |     | 3.3.8   | Packet Identifier Check                                       |

|   |     | 3.3.9   | Message Descriptor List (MEDL)                                |

|   | 3.4 | Fehler  | erkennungsmechanismen verschiedener Schnittstellen $$ . $$ 22 |

|   |     | 3.4.1   | RS-232                                                        |

|   |     | 3.4.2   | RS-485 Schnittstelle                                          |

|   |     | 3.4.3   | Enhanced Parallel Port (EPP)                                  |

|   |     | 3.4.4   | USB                                                           |

|   |     | 3.4.5   | Firewire                                                      |

|   |     | 3.4.6   | TTP/C                                                         |

|   |     | 3.4.7   | TTP/A                                                         |

|   |     | 3.4.8   | LVDS                                                          |

|   |     | 3.4.9   | Controller Area Network (CAN)                                 |

|              |          | 3.4.10 Ethernet                                                |

|--------------|----------|----------------------------------------------------------------|

|              | 3.5      | Integration von Fail-safe-Verhalten in Schnittstellen 32       |

| 4            | Den      | nonstrator 37                                                  |

|              | 4.1      | Bedeutung                                                      |

|              | 4.2      | Aufbau und Funktionsweise                                      |

|              | 4.3      | Implementierungskonzepte                                       |

|              |          | 4.3.1 Modellierung von Fail-safe-Verhalten 39                  |

|              |          | 4.3.2 Konstruktion des Interfaceblocks 40                      |

|              | 4.4      | Implementierung                                                |

|              |          | 4.4.1 Templates                                                |

|              |          | 4.4.2 Schnittstellen und ihre Verbindung 46                    |

|              |          | 4.4.3 Implementierung von Fail-safe-Verhalten 48               |

| 5            | Zus      | ammenfassung und Ausblick 53                                   |

| $\mathbf{A}$ | Que      | lltexte der Templates 55                                       |

|              |          | Interfaceblock (ifb.vhd)                                       |

|              |          | Controlunit (cu.vhd)                                           |

|              |          | Handler                                                        |

|              |          | A.3.1 Sequencehandler (shandler.vhd) 68                        |

|              |          | A.3.2 Protocolhandler_in (phandler_in.vhd)                     |

|              |          | A.3.3 Protocolhandler_out (phandler_out.vhd)                   |

|              | A.4      | Interruptswitch (intswitch.vhd)                                |

|              | A.5      | Handlercontrol (handlercontrol.vhd)                            |

|              | A.6      | Modeswitch (modeswitch.vhd)                                    |

|              |          | A.6.1 Generisches OR (g_or.vhd)                                |

|              | A.7      | Modus (modus.vhd)                                              |

|              | A.8      | Zusatzfunktionen (ifb_functions.vhd)                           |

| В            | Que      | lltexte zum Demonstrator 89                                    |

| _            | •        | Fail-safe-Interfaceblock (fs_ifb.vhd)                          |

|              |          | Controlunit (cu.vhd)                                           |

|              | <u>_</u> | B.2.1 Kontrollautomat Protocolhandler_in (phin_ctrl.vhd) 100   |

|              |          | B.2.2 Kontrollautomat Sequencehandler (sh_ctrl.vhd) 102        |

|              |          | B.2.3 Kontrollautomat Protocolhandler_out (phout_ctrl.vhd) 106 |

|              |          | B.2.4 Timer (timer_1sec.vhd)                                   |

|              |          | B.2.5 Taktgenerator (taktgen_9600Hz.vhd)                       |

|              | В.3      | Handler                                                        |

|              | B.4      | Modus für Protocolhandler_in (mod_phi_rs232.vhd) 110           |

|              |          | B 4 1 Paritätspriifer (parity check odd yhd) 114               |

| B.5 | Modus für Protocolhandler_out (mod_pho_epp.vhd) 116           |

|-----|---------------------------------------------------------------|

| B.6 | Normalmodus für Sequencehandler (mod_sh_normal.vhd) 119       |

| B.7 | Fail-safe-Modus für Sequencehandler (mod_sh_failsafe.vhd) 123 |

| B.8 | Roboterkontrolle und Steuerung                                |

|     | B.8.1 Robotersteuerung                                        |

|     | B 8 2 Roboterkontrolle 129                                    |

# Tabellenverzeichnis

| ,  | 3.1  | Systemzustände und ihr Verhalten                                 | 6  |

|----|------|------------------------------------------------------------------|----|

| ,  | 3.2  | Fehler und Fehlererkennung                                       | 19 |

|    |      |                                                                  |    |

| Al | obi  | ldungsverzeichnis                                                |    |

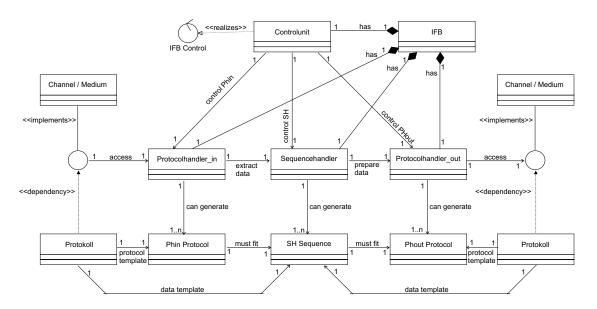

| 6  | 2.1  | Klassendiagramm des IFB                                          | 4  |

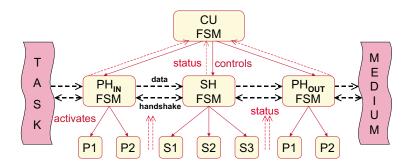

| 6  | 2.2  | Makrostruktur des IFB                                            | 5  |

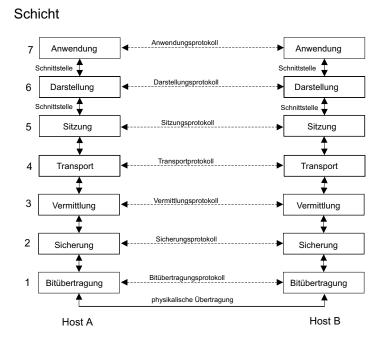

| 6  | 2.3  | Das ISO-OSI-Referenzmodell                                       | 7  |

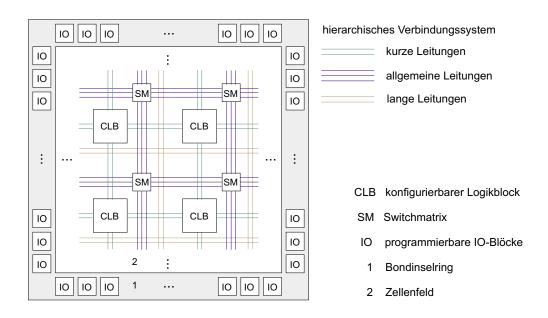

| 4  | 2.4  | Aufbau einer FPGA                                                | 9  |

| 4  | 2.5  | CLB Spartan 2E                                                   | 1  |

| 4  | 2.6  | IO-Block Spartan 2E                                              | 12 |

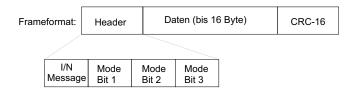

| ,  | 3.1  |                                                                  | 24 |

| ,  | 3.2  |                                                                  | 24 |

| ,  | 3.3  | Aufbau der Adresse von Firewire                                  | 25 |

| ,  | 3.4  | Aufbau einer TTP/C Node                                          | 26 |

| ,  | 3.5  | Aufbau der TTP/C MEDL                                            | 27 |

| ,  | 3.6  | TTP/C Frameformat                                                | 27 |

| ,  | 3.7  | Berechnung des CRC bei TTP/C                                     | 28 |

| ,  | 3.8  | CAN Datenrahmen                                                  | 30 |

| ,  | 3.9  | Aufgaben zur Erfüllung von Fail-safe-Verhalten in Schnittstellen | 32 |

| ,  | 3.10 | Fail-safe-Verhalten in einem IFB                                 | 34 |

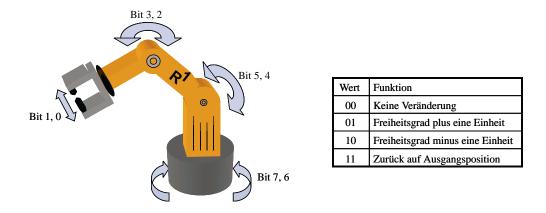

| 4  | 4.1  | Der Aufbau des Demonstrators                                     | 38 |

| 4  | 4.2  | Funktionen des Roboters                                          | 38 |

| 4  | 4.3  |                                                                  | 10 |

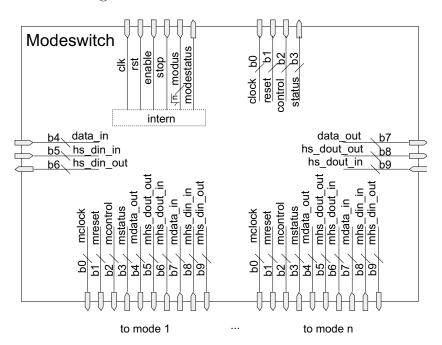

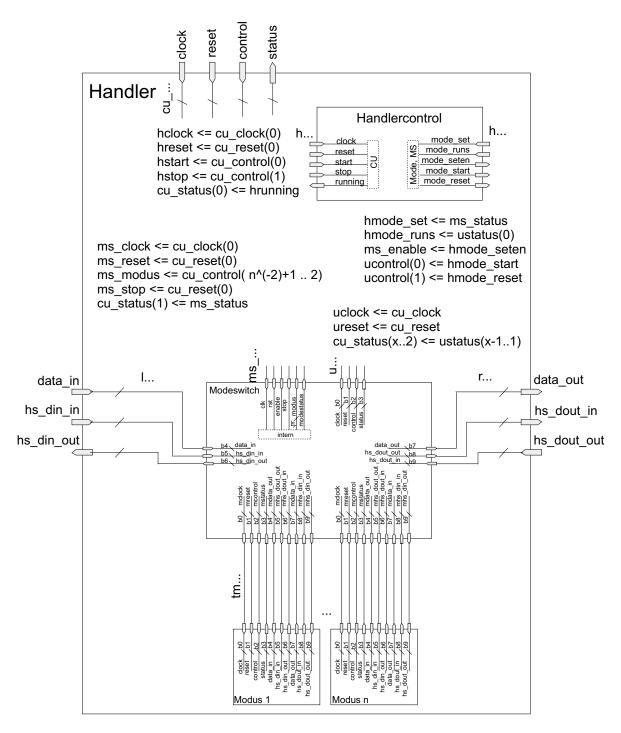

| 4  | 4.4  | Ports des Modeswitch                                             | 12 |

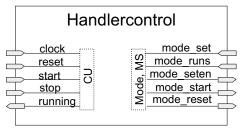

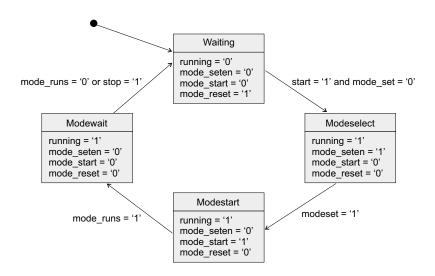

| 4  | 4.5  | Ports der Handlercontrol                                         | 13 |

| 4  | 4.6  | Automat der Handlercontrol                                       | 13 |

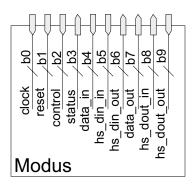

| 4  | 4.7  | Ports des Modus                                                  | 14 |

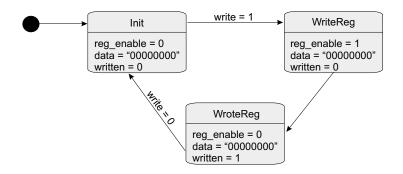

| 4  | 4.8  |                                                                  | 15 |

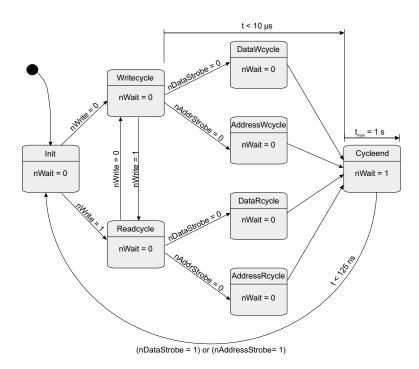

| 4  | 4.9  | Kommunikationsautomat des EPP-Protokolls                         | 16 |

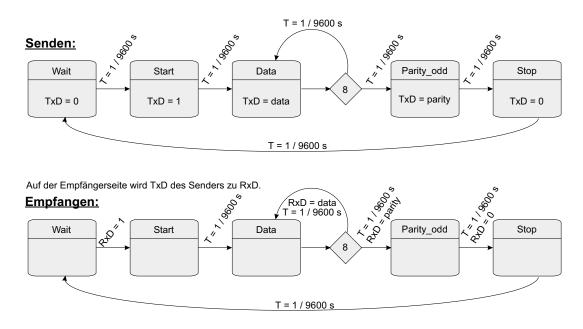

| 4  | 4.10 | Kommunikationsautomat RS-232                                     | 17 |

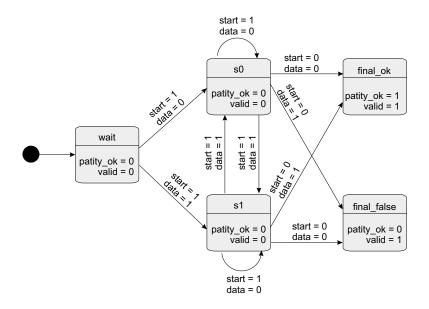

| 4  | 4.11 | Automat zur Paritätsprüfung                                      | 19 |

|    |      | 1 0                                                              | 50 |

|    |      |                                                                  | 51 |

## 1 Einführung

## 1.1 Aufgabenstellung

FPGAs sind konfigurierbare Hardwarekomponenten, die mittlerweile beachtliche Rechenleistung bereitstellen und eine große Anzahl an I/Os vorweisen. Die Herausforderung besteht im Einsatz von FPGA-Boards in eingebetteten Systemen unter Echtzeitbedingungen. Da Kommunikation nicht immer Echtzeitfähig gestaltet werden kann (z.B. Internet) soll ein FPGA als Kommunikationsmodul in einer nicht echtzeitfähigen Kette von Elementen eingebaut werden, um auch Komponenten mit harten Echtzeitbedingungen in eingebetteten Systemen einzubinden. Dabei übernimmt das FPGA-Board die Funktion, im Fall von zu großen Verzögerungen oder des Ausfalls des Kommunikationspartners, automatisch Fail-safe-Daten für die Komponenten mit harter Echtzeit zu generieren. Die Neuheit dieses Ansatzes besteht darin, das Fail-safe-Verhalten nicht erst in der Endkomponente sondern bereits in der verbindenden Schnittstelle und damit transparent für die Komponente zu erzeugen. Im Gegensatz zu Softwarelösungen bietet ein FPGA-Board die Möglichkeit des Rapid-Prototyping in Hardware.

## 1.2 Gliederung der Arbeit

Das 1. Kapitel enthält die Aufgabenstellung und einen kurzen Überblick über die Gliederung der Arbeit. Kapitel 2 betrachtet die Grundlagen, die zur Lösung der Aufgabenstellung notwendig waren. Dabei wird auf das Modell des Interfaceblocks und den Protokollbegriff eingegangen. Des Weiteren wird der Aufbau von FPGA's erklärt. Das 3. Kapitel betrachtet das Failsafe-Verhalten und zeigt verschiedene Möglichkeiten der Fehlererkennung allgemein und an verschiedenen Protokollen. Außerdem erklärt es, wie Failsafe-Verhalten in Schnittstellen integriert werden kann. Kapitel 4 stellt die Implementierung eines Demonstrators vor, in welchem die in dieser Arbeit vorgestellten Konzepte und Ergebnisse kombiniert und validiert werden. Das 5. Kapitel fasst die Ergebnisse der Arbeit zusammen und gibt einen Ausblick auf Weiterentwicklungsmöglichkeiten.

## 2 Grundlagen

In diesem Kapitel werden die Grundlagen betrachtet, die zur Lösung der Aufgabenstellung notwendig sind und zum Grundverständnis der folgenden Kapitel beitragen sollen. Als erstes wird das Modell des Interfaceblocks allgemein betrachtet und erklärt. Im Anschluß erfolgt die Erläuterung des Protokollbegriffs. Der Aufbau von FPGAs wird schließlich im letzten Teil des Kapitels beschrieben.

## 2.1 Das Modell des Interfaceblock (IFB)

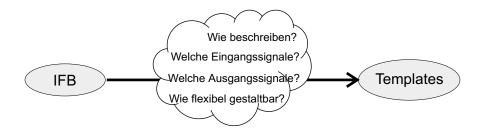

Der Interfaceblock (IFB) ist ein Modell, dass erstmals in der Diplomarbeit von Stefan Ihmor [Ihm01] vorgestellt wurde.

Das Konzept des IFB wurde erdacht, um Schnittstellen zwischen unterschiedlichen Kommunikationskomponenten automatisiert generieren zu können, ohne Änderungen an den Komponenten selbst vorzunehmen. Kommunikationskomponenten können einerseits komplexe Kommunikationsstrukturen, wie Bussystem, oder andererseits funktionale Komponenten wie Algorithmen sein. Diese werden in der IFB-Terminologie entsprechend als Medium bzw. Task bezeichnet.

Als Beispiele für ein Medium könnte der Anschluss eines Joysticks, die RS-232-Schnittstelle oder der PCI-Bus aufgeführt werden. Der Begriff Medium wird in diesem Zusammenhang nicht für die simple Verdrahtung der Schnittstellen von Task und Medium verwendet. Unterschiedliche Beispiele für Tasks könnten ein Analog-Digital-Wandler, ein JPEG-Encoder, oder auch die Steuerungen eines technischen Systems sein. Der Interfaceblock bietet die Möglichkeit Medien, Tasks oder eine Mischung aus Medien und Tasks miteinander zu verbinden. Da in einem Interfaceblock Daten zwischen Sender und Empfänder transformiert werden, kann dieser als Adapter zwischen physisch inkompatibel bzw. sematisch inkompatibel Kommunikationskomponenten eingesetzt werden. Dabei werden die physikalische Struktur, elektrische Eigenschaften und die Protokolle der Schnittstelle berücksichtigt.

Der Interfaceblock ist modular aufgebaut. Dies bringt einige entscheidende Vorteile mit sich. Beim Entwurf bietet es die Möglichkeit, die Arbeit zu unterteilen und diese dann später zusammen zu fügen. Weiterhin erhöht dieser

Ansatz die Wiederverwendbarkeit für andere Projekte. Dies spart Entwicklungszeit und -kosten. Eine weiterer Vorteil besteht darin, Intellectual Properties (IPs), also Komponenten von Drittanbietern, als Teil des IFB einzubinden. Die Vision des vorgestellten Konzepts ist eine voll-automatische Generierung von Schnittstellen in Form von Interfaceblöcken basierend auf einer XML-Beschreibung die in [Fic03] vorgestellt wird.

Abbildung 2.1: Klassendiagramm des Interfaceblocks

Der strukturelle und funktionale Aufbau eines IFB ist im Klassendiagramm in Abbildung 2.1 veranschaulicht. Die Struktur des Interfaceblock wird als Makrostruktur bezeichnet. Sie ist in Abbildung 2.2 dargestellt. Bestandteile des Interfaceblocks sind die Kontrolleinheit, zwei Protokollhandler und ein Sequenzhandler. Jeder Handler enthält mindestens einen Modus, der das dynamische Verhalten des Interfaceblocks implementiert. Im den folgenden Abschnitten werden diese einzelnen Komponenten in ihrem Aufbau und ihrer Funktionalität näher erläutert.

## 2.1.1 Die Kontrolleinheit (CU)

Die Kontrolleinheit (vgl. Abbildung 2.2) übernimmt die Steuerungsaufgaben innerhalb des Interfaceblocks. Sie koordiniert und kontrolliert die Funktionalität der Protokollhandler und des Sequenzhandlers. Dazu bestimmt

Abbildung 2.2: Makrostruktur des Interfaceblocks

die Kontrolleinheit den jeweils aktiven Modus eines Handlers, welcher die auszuführende Funktionalität implementiert, die mittels einer Automatenbeschreibung modelliert wurde. Das Wissen über den aktuellen Zustand der Schnittstelle bezieht die Kontrolleinheit aus Rückmeldungen in Form von Statussignalen aus den Handlern. Ein Teil der Steuerlogik in der Kontrolleinheit sind Timer, die die Zeitbasis der Schnittstelle implementieren. Dadurch ist es möglich den Interfaceblock als Echtzeitschnittstelle zu betreiben.

## 2.1.2 Die Protokollhandler (PH)

Die Protokollhandler sind die externen Schnittstellen des Interfaceblocks. Hier erfolgt die eigentliche Kommunikation mit allen verbundenen Tasks und Medien. Ein Protokollhandler kann, basierend auf seinen Modi, die Protokolle der jeweiligen Kommunikationskomponenten verarbeiten. Das beinhaltet das sowohl das Senden als auch das Empfangen von Daten.

Durch Umschalten zwischen unterschiedlichen Modi ist es möglich, verschiedene Protokolle zu verarbeiten. Der Handler fungiert hier als "Schalter", wobei die Modi für die eigentliche Generierung oder das Auslesen der Protokolle zuständig sind. Hierbei übernimmt der Protokollhandler die Funktion der Schnittstelle zwischen Kontrolleinheit und Modi sowie zwischen Kommunikaitonskomponente und Sequenzhandler. Dabei werden in einem Modus die Nutzdaten von dem redundanten Teil des Protokolls getrennt. Diese Nutzdaten werden dann an den Sequenzhandler weitergeleitet.

## 2.1.3 Der Sequenzhandler (SH)

Der Sequenzhandler ist das Bindeglied zwischen den Protokollhandlern des Interfaceblocks. Basierend auf einer Abbildungsvorschrift werden hier die eingehenden Nutzdaten konform zum ausgehenden Protokoll transformiert. Dazu nimmt der Sequenzhandler Daten vom eingehenden Protokollhandler entgegen und kann diese in Abhängigkeit vom ausgehenden Protokollhandler modifizieren. Dazu verfügt der Sequenzhandler über entsprechende Modi, die neben einer strukturellen Änderung von Daten auch eine semantische Änderung ermöglichen. So weden für den ausgehenden Protokollhandler fertige Datenpakete vorbereitet, die dieser dann nur noch in das Protokoll integrieren und versenden muss.

Wie schon der Protokollhander, bildet auch der Sequenzhandler die Schnittstelle zwischen seinen Modi und der Kontrolleinheit und führt den Wechsel dieser Modi aus. Die Steuerung übernimmt auch hier die Kontrolleinheit.

#### 2.1.4 Der Modus

Modi werden sowohl im Protokoll- als auch im Sequenzhandler benötigt. Sie realisieren das dynamische Verhalten des Interfaceblocks. Als frei definierbarer Automat verfügt ein Modus generell über keine festgelegte Funktionalität, es gibt allerdings einige Restriktionen, der den Aufbau des endlichen Automaten (FSM) reglementiert.

Als Instanz übernimmt ein Modus dann eine spezialisierte Aufgabe in einem Handler, wie oben beschrieben. Die direkte Steuerung eines Modus übernimmt der jeweilige Handler. Die eigenlichen Steuersignale dazu enstammen aber sämtlich der Kontrolleinheit. Trotz der einheitlichen Beschreibung als FSM realisiert ein Modus unterschiedliche Funktionalität als Protokollhandler bzw. Sequenzhandler.

Als Protokollhandlermodus übernimmt er die Verarbeitung eines Protokolls eines Mediums oder einer Task. Dabei implementiert der Modus einen Kommunikationsautomaten, der genau ein Protokoll verarbeiten kann. Dazu wird jeder Kommunikationsautomat als komplementäre Schnittstelle zur verbundenen Kommunikationskomponente erzeugt. Zur Protokollverarbeitung muss der Automat die empfangenen Nutzdaten über den Protokollhandler an den Sequenzhandler leiten und abgehende Daten, die er vom Sequenzhandler erhalten hat, konform in das entsprechende Protokoll integrieren. Durch die Anordnung mehrerer Modi in einem Protokollhandler und der Möglichkeit,

diese einzeln zu aktivieren, ist es möglich auf unterschiedliche Protokolle zuzugreifen.

Der Modus eines Sequenzhandlers muß nicht mit der externen Welt kommunizieren. Er übernimmt Transformationen auf den zwischen den Protokollhandlern transferierten Nutzdaten. Ein Sequenzhandlermodus kann Daten strukturell umwandeln, Berechnungen darauf ausführen und sogar neue Daten nach einem vorgegebenem Schema generieren. Die kurzzeitige Speicherung von Daten ist hier ebenfalls möglich. Ausgehend von einem einfachen Durchreichen der Daten bis hin zu komplexen Algorithmen, ist eine vielfältige Funktionalität in einem Sequenzgeneratormodus modellierbar.

## 2.2 Definition des Protokollbegriffs

Zur Definition des Protokollbegriffs, auf den in den folgenden Kapiteln noch häufiger eingegangen wird, ist zunächst die Betrachtung des Aufbaus von Netzwerken notwendig. In der Regel sind Netzwerke schichtenweise aufgebaut. Dies ist notwendig um die Komplexität bei der Entwicklung beherrschbar zu halten. Eine Standardisierung dieses Schichtenmodells, die von der

Abbildung 2.3: Das ISO-OSI-Referenzmodell

International Standards Organisation (ISO) entwickelt wurde, stellt das OSI-Referenzmodell (Abbildung 2.3) dar. OSI bedeutet Open System Interconnection, also Kommunikation offener Systeme. Das Modell beschreibt 7 hierarchische Schichten innerhalb eines Netzwerkes, die Bitübertragungs-, Sicherungs-, Vermittlungs-, Transport-, Sitzungs-, Darstellungs- und Anwendungsschicht. Eine sehr umfassende Darstellung des OSI-Refernzmodells ist in [Tan03] zu finden. Eine gute Zusammenfassung bietet [Wie]. In Abbildung 2.3 wird der Aufbau des OSI-Referenzmodells veranschaulicht. Allerdings ist es nicht immer möglich, eine Netzwerkarchitektur in die 7 Schichten zu unterteilen, da manchmal eine reale Schicht die Aufgaben von zwei oder mehr Modellschichten übernimmt.

Die Bitübertragungsschicht ist für die Übertragung der Bits über den Kommunikationskanal zuständig. In der Sicherungsschicht werden aus dem Bitstrom wieder Datenpakete gewonnen. Mit dem Routing der Pakete innerhalb des Subnetzes beschäftigt sich die Vermittlungsschicht. Die Transportschicht übernimmt Daten von der Sitzungsschicht und teilt sie, wenn nötig, in kleinere Teile auf. Sie wird auch dazu genutzt, um die Sitzungsschicht unabhängig von der Hardware zu halten. In der Sitzungsschicht können Vorkehrungen getroffen werden, um Verbindungen nach Abbrüchen wiederherstellen zu können. Außerdem steuert es die gerade laufende Sitzung hinsichtlich Dialogsteuerung, Token-Management und Synchronisation. In der Darstellungsschicht ist die Syntax und Semantik der übertragenen Daten von Bedeutung. Es können Datentypen definiert werden, Daten verschlüsselt oder entschlüsselt werden. In der letzten Schicht, der Anwendungsschicht, werden die Daten des Senderprozesses nun genutzt. In dieser Schicht sind eine Vielzahl von Anwendungsprotokollen definiert, wie zum Beispiel HTTP (Hyper Text Transfer Protocol), FTP (File Transfer Protocol) und SMTP (Simple Mail Transfer Protocol) auch besser bekannt als E-Mail.

Der theoretische Übertragungsweg erfolgt nur zwischen den gleichen Schichten bei Sender und Empfänger. Damit die Kommunikation innerhalb einer Schicht stattfinden kann, ist ein Protokoll nötig. Das Protokoll legt die Regel und Bestimmungen fest, nach denen die Kommunikation abläuft. Jede Schicht hat ihr eigenes Protokoll.

Die reale Kommunikation findet auf der Senderseite über die Schichten von oben nach unten statt. Die untere Schicht stellt jeweils für die übergeordnete Schicht einen Dienst bereit, der die Daten entgegennimmt und weiterleitet. Die Nachricht wird von der Anwendungsschicht bis zur Bitübertragungsschicht durchgereicht. Dabei werden die Daten von der oberen Schicht in das schichteigene Protokoll verpackt und als Nutzdaten an die darunterliegende

Schicht weitergegeben. Erst auf der Bitübertragungsschicht findet die eigentliche Datenübertragung statt. Auf der Empfängerseite wird die empfangene Nachricht dann Schicht für Schicht nach oben gereicht. Jede Schicht entfernt das aktuelle Transportprotokoll, extrahiert die Nutzdaten und reicht sie an die darüberliegende Schicht weiter.

Für die reale Kommunikation kann auch ein Interfaceblock (vgl. Abschnitt 2.1) zum Einsatz kommen. Er läßt sich in das ISO-OSI-Referenzmodell einordnen. Der Interfaceblock kann eine Verbindung zwischen den Schichten herstellen. Somit können Lücken zwischen den Schichten geschlossen werden, für die keine Implementierung existiert. Es ist aber auch möglich mit dem Interfaceblock ganze Schichten zu überbrücken.

## 2.3 FPGA

FPGA's (Field programmable Gate Array) sind programmierbare Hardwarebausteine und gehören zur Gruppe der anwenderprogrammierbaren Schaltungen. Mit ihnen ist die Realisierung von kombinatorischen und sequentiellen digitalen Schaltungen möglich. Im Allgemeinen bestehen FPGA's aus programmierbaren Logikblöcken (CLB) zur Realisierung von kombinatorischen

Abbildung 2.4: Der allgemeine Aufbau einer FPGA

und sequentiellen Schaltungen, konfigurierbaren I/O-Blöcken zur Kommunikation nach außen und einer programmierbaren hierarchischen Verbindungsstruktur, die die Logikblöcke untereinander und mit den I/O-Blöcken verbinden kann. Der Aufbau ist nocheinmal in Abbildung 2.4 veranschaulicht.

Zur Konfiguration der FPGA's existieren zwei verschiedene Technologien, die antifusebasierte und die SRAM-basierte. FPGA's mit Antifuses sind nur einmal konfigurierbar, da dort durch hohe Programmierspannungen Isolatorschichten zwischen zwei Leitungen aufgeschmolzen werden und somit eine leitende Verbindung entsteht. Der Vorteil dieser Technologie ist, das die Konfiguration nicht flüchtig ist. Wenn man den Strom abschaltet, dann bleibt sie bestehen. Außerdem sind Antifuses kleiner als SRAM-Zellen. Bei der SRAM-Technologie werden SRAM-Zellen als Speicher genutzt. Diese Zellen sind mit dem Gate eines Schalttransistor verbunden, der je nach Wert in der SRAM-Zelle leitend oder gesperrt ist. Der Nachteil dabei ist, dass die SRAM-Zellen ihren Wert verlieren, sobald der Strom abgeschalten wird. Um ein FPGA wieder in Betrieb zu nehmen, muss ein erneutes Laden der Konfiguration erfolgen. Allerdings ist es dadurch möglich, die FPGA mit anderen Konfigurationen zu laden. Dies eignet sich besonders zu Testzwecken in der Entwicklungsphase. Außerdem ist es vorteilhaft, wenn spätere Anderungen an der implementierten Funktionalität notwendig werden.

Ausführlichere Angaben zur Technologie von antifuse und SRAM-basierten FPGA's sind in [Wan98] und [Mül03] zu finden. Im Folgenden werden die Bestandteile einer SRAM-basierten FPGA näher erläutert. Dabei wird genauer auf die Komponenten der Spartan 2E von Xilinx eingegangen, da diese FPGA die Zielplattform des Demonstrators aus Kapitel 4 bildet.

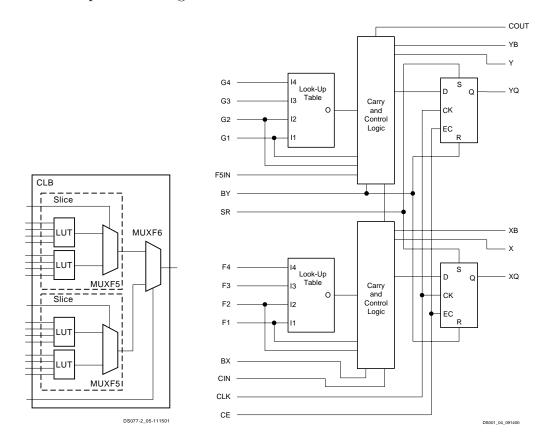

## 2.3.1 Konfigurierbare Logikblöcke

Die konfigurierbaren Logikblöcke (CLB) realisieren die kombinatorischen und sequentiellen Funktionen eines FPGA. Dies geschieht auf der Grundlage von Look-up-tables (LUT) und Flipflops. Die LUT's bestehen aus SRAM-Zellen, die abhängig von der Eingangsbelegung ausgelesen werden. Damit können sehr komplexe kombinatorische Funktionen mit einer konstanten Laufzeit realisiert werden, da die LUT eine konstante Zeit zum Auslesen des Wertes braucht. Bei einigen FPGA-Typen, wie dem Virtex-II von Xilinx [Xil03b], ist es außerdem möglich, die LUT's als RAM zu benutzen. Mit den Flipflops lassen sich sequentielle Schaltungen realisieren.

Die CLB's der Spartan 2E bestehen aus zwei gleichen Teilen. Jeder dieser Teile besitzt zwei LUT's mit jeweils 4 Eingängen, einer Carry und Control Logik für jede LUT und zwei Flipflops. Der Aufbau ist in Abbildung 2.5 veranschaulicht. Die LUT's des Spartan 2E können als LUT, RAM oder Schieberegister genutzt werden. Die Flipflops lassen sich als flankengetriggerte D-Flipflops oder als pegelgesteuerte Latches benutzen. Außerdem besitzt jeder Teil des CLB einen synchron oder asynchron betreibbaren Setz- und Rücksetzeingang. Eine Carry und Control Logik ermöglicht außerdem eine schnelle Implementierung von arithmetischen Funktionen.

Abbildung 2.5: Konfigurierbarer Logikblock einer Xilinx Spartan 2E FPGA, Quelle [Xil03a]

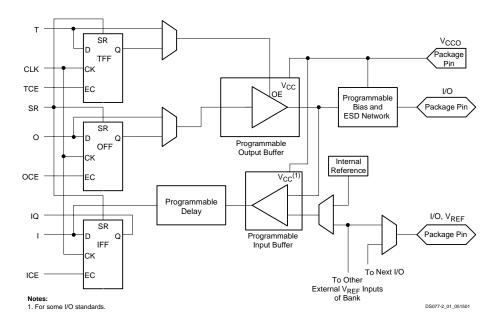

## 2.3.2 IO-Blöcke

Die IO-Blöcke stellen die Verbindung zwischen den Logikblöcken und der Außenwelt her. Ein IO-Block ist mit einem Pin des Gehäuses verbunden und hat verschiedene Betriebsmodi. Er kann so konfiguriert werden, dass er Eingang, Ausgang, oder Bidirektional ist. Es können verschiedene Pegel und Frequenzen konfiguriert werden. So kann man bei der Spartan 2E zum Beispiel direkt an einen PCI oder AGP-Bus gehen oder auch LVTTL (Low Voltage TTL) anbinden. Des Weiteren beinhalten IO-Blöcke Flipflops, womit es möglich ist, den Eingang zu puffern. Der Aufbau des IO-Blocks der Spartan 2E ist in Abbildung 2.6 zu sehen.

Abbildung 2.6: IO-Block einer Xilinx Spartan 2E FPGA, Quelle [Xil03a]

#### 2.3.3 Verbindungsstruktur

Im Allgemeinen haben FPGAs drei Arten von Verbindungsleitungen. Es gibt lange, kurze und allgemeine Leitungen. Das Routing erfolgt über Schalttransistoren an denen sich eine SRAM-Zelle befindet. Durch den Wert in der Zelle wird festgelegt, ob zwei Leitungen miteinander verknüpft werden oder nicht. Der Nachteil der Schalttransistoren ist, dass sich mit jedem Transistor eine Verzögerungszeit zur Leitungsverzögerung addiert. Die Geschwindigkeit der Schaltung wird letzendlich durch die größte Leitungsverzögerung, die den kritischen Pfad bildet, bestimmt. Deshalb wird beim Routing versucht, die Leitungen so schnell wie möglich zu halten, also so wenige Schalttransistoren wie möglich zu benutzen. Die drei Leitungsarten des FPGA haben deshalb

auch unterschiedliche Eigenschaften ihre Länge und Routingmöglichkeiten betreffend.

Die langen Leitungen dienen dazu, Signale über große Distanzen zu routen. Sie verlaufen horizontal und vertikal durch das FPGA. Lange Leitungen haben wenige potentielle Verbindungspunkte zu den CLB und müssen somit nur wenige Schalttransistoren überwinden. Das wirkt sich positiv auf die Signallaufzeiten aus. Allerdings gibt es nur eine relativ geringe Anzahl dieser Leitungen innerhalb des FPGA.

Kurze Leitungen werden verwendet, um Verbindungen von einem CLB zu einem benachbarten herzustellen. Außerdem stellen sie Verbindungen zwischen CLB und Switchmatrix her, um Signale auch über benachbarte CLBs hinaus zu transportieren. Ihre Länge ist gering. Dafür sind aber schnelle Verbindugnen möglich.

Mit den **allgemeinen Leitungen** ist ein Routing zwischen den Switchmatrizen möglich. Switchmatrizen sind programmierbare Verbindungsstrukturen. Die Verbindungen werden wieder über Schalttransistoren realisiert. Aus diesem Grund sind die allgemeinen Leitungen die langsamsten aber auch die flexibelsten Verbindungsstrukturen eines FPGA.

Bei der Spartan 2E gibt es auch diese drei Arten von Leitungen. Die kurzen Leitungen, oder lokale Leitungen wie sie im Datenblatt [Xil03a] genannt werden, können Verbindungen zu benachbarten CLBs oder zur Switchmatrix (Routingmatrix) herstellen. Sie können aber auch rückgekoppelt werden. Die allgemeinen Leitungen verlaufen immer zwischen banachbarten Routingmatrizen. Von jeder Routingmatrix gehen je 24 Leitungen nach links, rechts, oben und unten. Zusätzlich gibt es noch gepufferte Leitungen, die über eine Länge von sechs CLB's verlaufen und auf die nur an den Endpunkten oder in der Mitte zugegriffen werden kann. Globale Leitungen gibt es je 12 Stück pro Spalte und Zeile. Sie verlaufen über die gesamte Länge des FPGA. Eine zusätzliche Verbindungsstruktur bildet der VersaRing. Er verbindet die IO-Blöcke mit dem CLB-Feld. Das Spartan 2E FPGA bietet des weiteren die Möglichkeit einen On-Chip 3-State-Bus zu realisieren. Außerdem gibt es 4 globale primäre Taktnetze, von denen jedes alle CLB's und IO-Blöcke treiben kann. Sie sind mit fest zugeordneten Eingangspins verbunden. Das sekundäre globale Netz ist nicht an bestimmte Pins gebunden. Es besteht aus 24 Leitungen, 12 oben und 12 unten im Chip, die zusammen mit den langen Leitungen auch alle CLB's erreichen können.

## 3 Fail-safe-Verhalten

In diesem Kapitel wird auf das Fail-safe-Verhalten einer Schnittstelle eingegangen. Der erste Teil befaßt sich mit der Begriffseinordnung und der Bedeutung des Themas. Anschließend werden mögliche Fehler bei Schnittstellen betrachtete und Maßnahmen zu ihrer Erkennung vorgestellt. Der Einsatz dieser Maßnahmen wird an einigen existierenden Schnittstellen vorgestellt. Als Abschluss wird die Integration von Fail-safe-Verhalten in Schnittstellen vorgestellt und am Modell des Interfaceblocks aus Abschnitt 2.1 beschrieben.

## 3.1 Einordnung und Bedeutung

Mit zunehmenden Fortschritt werden technische Systeme immer komplexer. Jedoch bringt eine höhere Komplexität auch meist eine größere Anfälligkeit für Fehler mit sich. Vor allem bei sicherheitskritischen Anwendungen, zum Beispiel in der Automobilelektronik, der Signalgebung und Kommunikation für die Eisenbahn, in Kernkraftwerken, bei der Steuerung von Flugzeugen, der Luftraumkontrolle, in der Medizin und für militärische Anwendungen, ist es deshalb wichtig, sich mit der Zuverlässigkeit solcher Systeme auseinanderzusetzen. Zuverlässigkeit ist nach DIN 40041 [iDuV90] Teil 1 die Gesamtheit derjenigen Eigenschaften einer Betrachtungseinheit, welche sich auf die Eignung zur Erfüllung gegebener Erfordernisse unter vorgegebenen Bedingungen für ein gegebenes Zeitintervall beziehen. Eine geringer Zuverlässigkeit erhöht die Wahrscheinlichkeit von Ausfällen. Ein Ausfall ist nach DIN 40041 Teil 3 das Aussetzen der Ausführung der festgelegten Aufgabe einer Betrachtungseinheit aufgrund einer in ihr selbst liegenden Ursache und im Rahmen der zulässigen Beanspruchung. Ein Fehler ist die Nichterfüllung vorgegebener Forderungen durch einen Merkmalswert (DIN 40041 Teil 3). Tritt ein Fehler auf, so findet eine unzulässige Abweichung eines Merkmals des Systems statt und es befindet sich somit in einem unzulässigen Zustand. Daraus folgt, dass ein Fehler auch ein Zustand des Systems ist.

Allgemein unterscheidet man bei Systemen verschiedene Arten von Betriebszuständen im Zusammenhang mit Fehlern. Tabelle 3.1 stellt eine Übersicht über die möglichen Zustände eines System und sein Verhalten im jeweiligen Zustand dar. Im Folgenden wird näher auf den Zustand Fail-safe eingegangen, zu dem auch Fail-stop-safe gehört.

Fail-safe bedeutet allgemein nach [Har03b] und [Gör89], ein System beim Auftreten eines Fehlers in einen sicheren Zustand zu bringen. Es wird nur

| Systemzustand    | Verhalten des Systems               |  |  |

|------------------|-------------------------------------|--|--|

| go               | System arbeitet sicher und korrekt  |  |  |

| fail-operational | System arbeitet fehlertolerant      |  |  |

|                  | ohne Leistungsverminderung          |  |  |

| fail-soft        | Systembetrieb ist sicher,           |  |  |

|                  | aber Leistung ist vermindert        |  |  |

| fail-safe,       | nur Systemsicherheit gewährleistet, |  |  |

| fail-stop-safe   | evtl. keine Systemleistung          |  |  |

| fail-unsafe      | unvorhersehbares Systemverhalten    |  |  |

Tabelle 3.1: Systemzustände und ihr Verhalten, nach [Gör89]

die Systemsicherheit gewährleistet, jedoch nicht zwingend die weitere Arbeit des Systems. Damit wird vermieden, dass ein unvorhersehbares Systemverhalten eintritt. Ein System wird in einen sicheren Zustand gebracht, wenn eine Fehlfunktion das System negativ beeinflußt und infolge der Beeinflussung Personenschäden, Materialschäden oder Zerstörungen am System entstehen können. Eine Fehlfunktion in einem System kann zum Beispiel durch den Ausfall eines Teilsystems, fehlerhafte Eingangssignale oder auch ausbleibende Signale verursacht werden.

Es gibt verschiedene Arten von sicheren Zuständen. Man kann das System einfach abschalten. Dies wird zum Beispiel bei den Bremsen eines Lkw gemacht. Die Bremsen werden durch Luftdruck gelöst und blockieren damit die Räder nicht. Falls der Luftdruck infolge eines Defektes abfällt, schließen sich die Bremsen und bringen den Lkw zum Stillstand.

Eine andere Möglichkeit wird bei Ampelanlagen eingesetzt. Sie besteht darin, ein Reservesystem zu aktivieren, welches die Steuerung übernimmt. An Ampelanlagen sind dies die zusätzlich angebrachten Verkehrsschilder, die die Vorfahrt regeln, wenn die Ampel nicht funktioniert.

Bei einem digitalen System könnten bei fehlerhaften Eingangssignalen von einer Steuerung undefinierte Zustände entstehen und somit ein unvorhergesehenes Verhalten auslösen. Zur Vermeidung dieses Problems können die Eingangssignale mit Prüfmechanismen versehen werden. Mit deren Hilfe ist eine Fehlererkennung auf den Eingangssignalen möglich. Fehlerhafte Signale werden nicht an das zu steuernde System weitergeleitet und somit undefinierte Zustände vermieden.

Der Einsatz von Fail-safe-Verhalten bietet sich bei Systemen an, bei denen der Einsatz redundanter Komponenten nicht möglich ist, sich nicht lohnt oder zu teuer wäre. Sie bieten somit eine günstige Variante für Systeme, bei denen die Systemleistung im Fehlerfall nicht garantiert sein muss, sondern nur eine Vermeidung von undefinierten oder gefährlichen Zuständen gewährleistet werden soll. Für den Einsatz von Fail-safe-Verhalten ist allerdings eine gute Kenntnis des Systems notwendig. Dazu gehört, dass man weiß, welche Fehler auftreten können, wie die Anwesenheit und das Auftreten von Fehlern erkennbar ist und welche Maßnahmen im Fehlerfall zu treffen sind. Durch diese Erfordernisse ist Fail-safe-Verhalten anwendungsabhängig.

## 3.2 Arten von Fehlern bei Schnittstellen

Bei Fehlern unterscheidet man nach [Gör89] drei Arten. Die erste Art sind Entwurfsfehler. Sie entstehen vor der Inbetriebnahme eines Systems. Zu ihnen zählen Implementierungsfehler, Spezifikationsfehler und Dokumentationsfehler. Die zweite Gruppe sind die Herstellungsfehler. Sie entstehen bei der Fertigung eines Systems zum Beispiel durch Fehler in der Fertigungstechnologie. Die dritte Art von Fehlern sind Betriebsfehler. Sie treten erst in der Nutzungsphase eines Systems auf. Zu ihnen zählen zufällige physikalische Fehler, Verschleißfehler, störungsbedingte Fehler, Bedienfehler, Wartungsfehler und absichtliche Fehler. Die Entwurfsfehler und Herstellungsfehler müssen beim Entwurfs- und Fertigungsprozess analysiert und vermieden werden. Hier ist nur ein System in der Nutzungsphase von Interesse, da Fail-safe-Verhalten zur Verhinderung von Fehlern dieser Phase eingesetzt werden.

Um Fail-safe-Verhalten vernünftig einsetzen zu können, ist zunächst eine Untersuchung der Fehler anzustellen, die auftreten können. Das Untersuchungsfeld wird sich hier auf Schnittstellen und die damit verbundene Datenübertragung zwischen zwei Systemen beschränken.

Bei der Datenübertragung müssen nach DIN EN 61508 VDE [iDuV02] Übertragungsfehler, Wiederholung, Verlust, Einfügung, falsche Abfolge, Nachrichtenverfälschung, zeitliche Verzögerung und Maskierung als mögliche Fehler angenommen werden. Übertragungsfehler sind Fehler, die während der Übertragung einer Nachricht auftreten und zum Beispiel durch elektromagnetische Einflüsse hervorgerufen werden. Eine Wiederholung liegt dann vor, wenn eine bereits gesendete Nachricht zu einem späteren Zeitpunkt fälschlicherweise wiederholt wird. Ein Verlust tritt ein, wenn eine Nachricht komplett gelöscht wird. Die Ursachen können beim Sender, der eine Nachricht nicht verschickt, beim Empfänger, der die Nachricht nicht annimmt oder im Nichtbestehen einer Verbindung liegen. Das Einfügen stellt eine nicht erlaubte Er-

weiterung der Daten einer Nachricht dar. Der Fehler der falschen Abfolge ereignet sich, wenn eine zeitlich ältere Nachricht nach einer neueren ankommt. Wird eine Nachricht verfälscht bevor sie mit einem Sicherungsmechanismus versehen oder geprüft worden ist, dann liegt eine Nachrichtenverfälschung vor. Eine zeitliche Verzögerung liegt vor, wenn die Nachricht zu einem bestimmten Zeitpunkt eintreffen muss, sie diesen aber verfehlt und später den Empfänger erreicht. Bei der Fehlermaskierung findet eine Verfälschung der Empfängeradresse statt. Dadurch erhält der falsche Empfänger die Nachricht.

## 3.3 Möglichkeiten der Fehlererkennung

Im vorigen Abschnitt wurden Arten von Fehlern vorgestellt, die bei der Datenübertragung auftreten können. Für den Einsatz von Fail-safe-Verhalten ist es jetzt notwendig, Möglichkeiten der Fehlererkennung zu betrachten. Dadurch kann man die Anwesenheit und das Auftreten von Fehlern erkennen und darauf entsprechend reagieren. Tabelle 3.2 fasst die Ergebnisse des Abschnittes zusammen und gibt eine Übersicht darüber, welcher Fehler durch einen bestimmten Fehlererkennungsmechanismus auffindbar sind.

#### 3.3.1 Parität

Die Paritätsprüfung dient zur Identifizierung von Übertragungsfehlern. Dabei wird beim Sender zusätzlich zu den Daten ein Prüfbit generiert, das anzeigt, wieviele Einsen der Datensatz enthält. Die Parität kann gerade (Summe der Bits gerade) oder ungerade (Summe der Bits ungerade) sein. Mit diesem Verfahren ist keine Fehlerkorrektur möglich. Es lassen sich nur Fehler erkennen, die eine ungerade Bitanzahl betreffen (1, 3, 5, ... Bit-Fehler).

## 3.3.2 Rechteckcode

Beim Rechteckcode werden mehrere Codewörter zugleich betrachtet. Aus den Codewörtern wird eine Matrix gebildet und darin für jede Spalte und Zeile ein Prüfbit generiert. Außerdem wird aus den Prüfbits ein weiteres Bit gebildet, das Eckbit. Bei diesem Schema verändert jeder Einzelfehler zwei Prüfbits. Somit lassen sich mit dem Rechteckcode 1-Bit Fehler korrigieren. Er kann aber auch 2-Bit und gewisse 3-Bit Fehler erkennen. Mit ihm lassen sich Übertragungsfehler identifizieren und auch Fehler durch Einfügung, da mehrere Codewörter betrachtet werden.

| $egin{array}{c} 	ext{Fehler} \ 	ext{Mechanismus} \end{array}$ | Übertragungsfehler | Wiederholung | Verlust | Einfügung | falsche Abfolge | Nachrichtenverfälschung | zeitliche Verzögerung | Maskierung |

|---------------------------------------------------------------|--------------------|--------------|---------|-----------|-----------------|-------------------------|-----------------------|------------|

| Parität                                                       | X                  |              |         |           |                 |                         |                       |            |

| Rechteckcode                                                  | X                  |              |         | X         |                 |                         |                       |            |

| Hammingcodes                                                  | X                  |              |         | X         |                 |                         |                       |            |

| Zyklische Codes                                               | X                  |              |         | X         |                 |                         |                       |            |

| Frame-Check                                                   | X                  |              |         | X         |                 |                         |                       |            |

| ACK-Fehler-Erk.                                               |                    | X            | X       |           | X               |                         |                       |            |

| Monitoring                                                    | X                  |              |         |           |                 |                         |                       |            |

| PID-Check                                                     | X                  |              |         | X         |                 |                         |                       |            |

| MEDL                                                          |                    | X            | X       |           | X               |                         | X                     |            |

Tabelle 3.2: Fehler und ihre Erkennung durch verschiedene Mechanismen

## 3.3.3 Hammingcodes

Hammingcodes verfolgen die Idee, dass die Prüfbits die Position des Fehlers im Codewort angeben. Das Codewort wird gespreizt und Prüfbits eingefügt. Die Prüfbits werden zur Paritätskontrolle von bestimmten Bits benutzt. Bei der Kontrolle des Codewortes wird eine Binärzahl, deren Länge der Anzahl Prüfbits entspricht, gebildet. Sie gibt die Position eines 1-Bit Fehlers genau an. Mit diesem Verfahren lassen sich Übertragungsfehler erkennen. Auch manche Einfügungen sind identifizierbar, da durch sie die Position der Prüfbits verändert wird.

## 3.3.4 Zyklische Codes (CRC)

Der Cyclic Redundancy Check basiert auf dem Prinzip Bitfolgen als Darstellung eines Polynoms P(x) mit den Koeffizienten 0 und 1 zu betrachten. Zusätzlich benötigt man noch ein Generatorpolynom G(x) vom Grad g. Das

Polynom T(x), das übertragen wird, besteht aus der Nachricht M(x) und einer angehängten Prüfsumme. Das Polynom P(x) wird mit  $x^g$  multipliziert. Das Produkt wird durch das Generatorpolynom G(x) dividiert. Es entsteht das Quotientenpolynom Q und ein Divisionsrest R. An die ursprüngliche Nachricht wird der Divisionsrest R angefügt und diese gesendet.

Der Empfänger teilt die Nachricht dann wieder durch G(x) und erhält den Rest R. Stimmt der Rest nicht mit den letzten Stellen der erhaltenen Nachricht überein, dann ist die Nachricht falsch.

Es gibt verschiedene standardisierte Generatorpolynome für unterschiedliche Codelängen. Zum Beispiel das CRC-16 Generatorpolynom nach ISO lautet  $x^{16} + x^{15} + x^2 + 1$ . Es erkennt alle einfachen und zweifachen Bitfehler, alle Fehler mit ungerader Bitanzahl und alle Fehlerbündel mit 16 oder weniger Bits. Außerdem ist es in der Lage 99,997 Prozent aller 17-Bit Fehlerbündel und 99,998 Prozent aller Fehlerbündel mit 18 oder mehr Bits zu erkennen. Ein weiterer Vorzug des CRC ist, dass die Prüfsummen hardwaremäßig mit einer einfachen Schieberegisterschaltung berechnet und ausgewertet werden können.

Mit zyklischen Codes lassen sich Übertragungsfehler sowie Einfügungen erkennen. Mehr Informationen zu zyklischen Codes bieten [Tan03] und [Gör89].

#### 3.3.5 Frame-Check

Der Frame-Check basiert auf der Struktur der übertragenen Nachricht und erkennt Fehler im Nachrichtenformat. Diese können durch Übertragungsfehler oder Einfügung auftreten. Zur Fehlererkennung wird der Rahmen der beim Empfänger eingehenden Nachricht überprüft. Die Kontrolle beschränkt sich dabei auf die Länge des Rahmens sowie der Korrektheit des Rahmenformates. Der Nutzdatenbereich einer Nachricht wird mit diesem Verfahren nicht kontrolliert.

#### 3.3.6 ACK-Fehler Erkennung

Acknowledgement Fehler (Bestätigungsfehler) sind Fehler, die bei Protokollen mit Quittierungsmechanismus auftreten können. Auf ein eingehendes Paket reagiert der Empfänger, indem er eine Antwort an den Sender schickt. Er quittiert also, dass er das Paket erhalten hat. Erhält der Sender keine Antwort auf ein gesendetes Paket kann das folgende Ursachen haben. Das

Paket ist nicht beim Empfänger angekommen infolge von zum Beispiel Leitungsstörungen. Das Paket ist beim Empfänger angekommen, jedoch ist die Antwort auf dem Weg zum Sender verlorengegangen oder gestört worden, so dass die Antwort nicht korrekt ist. Eine weitere Ursache kann darin liegen, dass das Paket zwar beim Empfänger angekommen ist, jedoch durch andere Fehlererkennungsmaßnahmen als fehlerhaft identifiziert wurde. In diesem Fall gibt es zwei Möglichkeiten. Der Empfänger kann zum Einen dem Sender eine Fehlernachricht schicken, zum Anderen auch nichts tun und sich darauf verlassen, dass der Sender die Nachricht noch einmal schickt. Der ACK-Fehler muss immer vom Sender identifiziert werden. Im Fehlerfall schickt der Sender die Nachricht erneut auf den Weg. Hat der Empfänger diese aber schon bekommen, ist also das ACK-Paket verlorengegangen, dann schickt der Empfänger eine Quittung, ignoriert aber die neue Nachricht.

#### 3.3.7 Monitoring

Das Monitoring beruht auf der Beobachtung der Buspegel durch den Sender. Der Sender kann Differenzen zwischen dem gesendeten und empfangenen Bit erkennen. Mit diesem Mechanismus ist es möglich alle globalen Fehler zu registrieren. Zusätzlich erlaubt es das Erkennen aller lokal am Sender auftretenden Bitfehler.

#### 3.3.8 Packet Identifier Check

Der Packet Identifier Check (PID-Check) überprüft die Paketidentifizierung auf Korrektheit. Dabei wird beim Sender das Einerkomplement des PID mit der Länge n gebildet und an sie angehangen. Es wird ein PID der Länge 2·n übertragen. Der Empfänger bildet wieder das Einerkomplement der letzen n Bits und vergleicht sie mit den ersten n Bits. Stimmen diese nicht überein, dann ist eine Übertargunsfehler aufgetreten. Dieses Verfahren kann aber nur bei paketorientierten Übertragungsverfahren mit Identifikatoren für jedes Paket angewendet werden. [USB00]

#### 3.3.9 Message Descriptor List (MEDL)

Eine Message Descriptor List (MEDL) ist ein Ein- und Ausgangsspeicher, der verschiedene Informationen enthalten kann. In ihr werden die Nutzdaten gespeichert, die gesendet oder empfangen werden sollen. Die Auslösung des Sendevorgangs kann durch einen Timer zu einer bestimmten Zeit oder mit dem Schreiben der Daten in die MEDL erfolgen.

Der Empfänger der Nachricht wird nicht direkt angegeben. Dies erfolgt über Descriptoren. Sie werden vor den Nutzdaten übertragen. In der MEDL der Empfänger ist der Descriptor auch gespeichert. Stimmt der Descriptor auf der Leitung mit einem in der MEDL überein, so wird die Nachricht entgegengenommen ansonsten ignoriert.

Benutzt man ein bestimmtes Protokoll, dann ist die Struktur der Message Descriptor List vorgegeben und somit auch ihre Fehlererkennungsmechanismen. Entwirft man eine MEDL, dann ist es dem Entwickler überlassen, welche Mechanismen er einbaut. Dadurch ist es möglich, Fehlerkennungsmechanismen für Wiederholungen, Verluste, falsche Abfolge und zeitliche Verzögerung einzubauen.

## 3.4 Fehlererkennungsmechanismen verschiedener Schnittstellen

In diesem Abschnitt wird eine Auswahl von Protokollen hinsichtlich ihrer Fehlererkennungsmechanismen untersucht. Somit kann man für die Fehlererkennung auf bereits in den Protokollen existierende Verfahren zurückgreifen, ohne Eigenentwicklungen vornehmen zu müssen.

## 3.4.1 RS-232

RS-232 ist ein Protokoll zur seriellen point-to-point Übertragung von Daten. Auf dieser Übertragungsart sind verschieden aufgebaute Datenpakete definiert. Die übertragenen Rahmen bestehen immer aus einem Startbit, das den logischen Pegel 1 hat. Anschließend folgen 7 oder 8 Datenbits an die sich ein Paritätsbit anschließen kann. Den Abschluss des Rahmens bilden 1 oder 2 Stoppbits mit dem logischen Pegel 0.

Bei der RS-232-Schnittstelle kann ein Paritätsbit eingesetzt werden, um Übertragungsfehler zu erkennen. Die Schnittstelle unterstützt dabei gerade und ungerade Parität.

#### 3.4.2 RS-485 Schnittstelle

Die RS-485-Schnittstelle ist ein serielles Bussystem. In der Spezifikation [Thi94] wird kein spezielles Protokoll definiert, sondern nur Übertragungsparameter. Das System basiert auf der Datenübertragung mittels eines Leitungpaares. Daran werden die bis zu 32 Endgeräte parallel angeschlossen. Die Daten werden durch Spannungsdifferenzen übermittelt. Durch die fehlende Protokolldefinition sind auch keine Fehlererkennungsmechanismen in der Spezifikation verzeichnet. Für die Fehlererkennung ist der Anwender selbst verantwortlich, da sich diese nach dem Protokoll richted, welches der Anwender implementiert.

## 3.4.3 Enhanced Parallel Port (EPP)

Das EPP Protokoll wurde für die parallele Übertragung mit der Centronics Schnittstelle entwickelt. Es ist ein Teil des IEEE 1284 Standards. Es erlaubt eine Datenrate von bis zu 2 Megabyte pro Sekunde. Dabei werden 8 Bit parallel gesendet. Die Synchronisation zwischen Sender und Empfänger erfolgt über Handshakesignale. Das EPP Protokoll definiert 4 Transferarten. Sie heißen Address-write, Data-write, Address-read und Data-read. Die Auswahl erfolgt über unterschiedliche Handshakeleitungen. Fehlererkennungsmechanismen sind bei keinem der Transferarten in der Spezifikation vorgesehen. Mehr zu den Transferarten und zur parallelen Schnittstelle steht in [Axe97] und in [EPP].

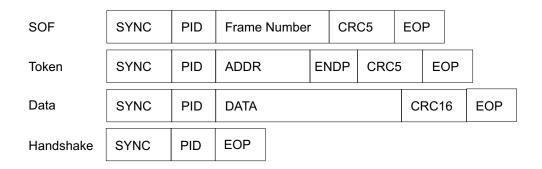

#### 3.4.4 USB

USB (Universal Serial Bus) ist ein serielles Bussystem von dem die Versionen 1.0, 1.1 und 2.0 definiert sind. In der grundlegenden Arbeitsweise unterscheiden sie sich jedoch nicht, weshalb hier nicht auf die einzelnen Versionen eingegangen wird. Die Daten werden seriell, also Bit für Bit, übertragen. Das Kabel besitzt dazu zwei Datenleitungen. Mit diesen wird das Signal differentiell übertragen, das heißt der Wert des Signals ist die Spannungsdifferenz zwischen den Datenleitungen. Durch dieses Verfahren wird die Störanfälligkeit des Kabels verringert. Die Topologie ist eine gemischte Sternund Strang-Bus-Technologie. Sie wird als Tiered-Star-Topologie bezeichnet. An einen Host können so bis zu 127 Endgeräte teilweise direkt oder über Hubs angeschlossen werden.

Abbildung 3.1: Aufbau der USB-Pakete

USB unterscheidet zwischen vier verschiedenen Paketen. Der Aufbau der einzelnen Pakete ist in Abbildung 3.1 veranschaulicht. Jedes Paket enthält immer ein SYNC-Feld, das zur Synchronisation dient. Des Weiteren ein PID (Packet Identifier) -Feld. Es gibt Auskunft über den Pakettyp, das Format des Paketes und den Typ der Fehlererkennung. Am Ende jedes Paketes befindet sich das EOP (End of Packet) -Feld, welches das Ende eines Paketes kennzeichnet. Als Synchronisationspaket dient das SOF (Start of Frame) -Paket. Es enthält die Nummer des nächsten Frames und eine 5-Bit Prüfsumme. Mit dem Token-Paket bestimmt der Host, welches Gerät als nächstes das Senderecht erhält. Es enthält die Adresse des Gerätes, das Endpoint-Feld, womit eine Adressierung einer Funktion des Gerätes möglich ist, und eine 5-Bit Prüfsumme. Das Data-Paket enthält die eigentlichen Nutzdaten und eine 16-Bit Prüfsumme. Zur Bestätigung eines Datenpaketes wird das Handshake-Paket eingesetzt.

| Р | PID 0 | PID 1 | PID 2 | PID 3 | PID 0 | PID 1 | PID 2 | PID 3 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|---|-------|-------|-------|-------|-------|-------|-------|-------|

Abbildung 3.2: Format eines USB PID, Quelle [USB98]

Die Verfahren zur Fehlererkennung sind bei USB 1.0, 1.1 und 2.0 gleich. Zur Fehlererkennung wird der Cyclic Redundancy Check (CRC) eingesetzt. USB unterstützt zwei Arten des CRC. Für die SOF- und Token-Pakete wird CRC5 mit dem Generatorpolynom  $G(x) = x^5 + x^2 + 1$  eingesetzt. Die Datenpakete werden durch CRC16 geschützt. Es verwendet das Generatorpolynom

$G(x) = x^{16} + x^{15} + x^2 + 1$ . Der CRC schützt alle Felder eines Paketes außer dem PID-Feld.

Das PID-Feld hat einen eigenen Schutzmechanismus. Von dem 4-Bit langen PID wird das Einerkomplement gebildet und an das Original angehängt. So ergibt sich die in Abbildung 3.2 gezeigte Struktur des PID. Wird eine fehlerhafte PID von einem Empfänger erkannt, dann ignoriert sie dieser.

Der dritte Fehlererkennungsmechanismus bei USB richtet sich gegen Acknowledge-Fehler. Zu diesem Zweck werden die Handshake-Pakete eingesetzt. Sie übermitteln den Status einer Datenübertragung und können Informationen über einen erfolgreichen Datenempfang, über eine Kommandoakzeptanz oder -zurückweisung, zur Flusskontrolle und zur Unterbrechungsanforderung enthalten.

Weiterführende Informationen zu USB sind in [USB98] und [USB00] zu finden.

#### 3.4.5 Firewire

Firewire ist ein serielles Hochgeschwindigkeitsprotokoll. Es kann aus bis zu 1023 Bussegmenten mit je 63 Geräten bestehen. Die Kommunikation zwischen den Geräten kann über Nachrichten (isochroner Modus) oder als verteilter Speicher (asynchroner Modus) erfolgen. Dabei können die Geräte direkt miteinander kommunizieren und müssen nicht über den Host Daten austauschen, wie bei USB.

|   | Busnummer | Gerätenummer | Adresse im Gerät |

|---|-----------|--------------|------------------|

| 0 | 9         | 10 15        | 16 63            |

Abbildung 3.3: Aufbau der Adresse von Firewire

Die angesteuerte Adresse setzt sich aus 10 Bit für das Bussegment, 6 Bit für die Geräte (Nodes) im Busegment und 32 Bit für die Adresse im Gerät zusammen (Abbildung 3.3). Die Datenübertragung ist in Runden organisiert. Die Dauer einer Runde beträgt 125  $\mu$ s. Den Start einer Runde signalisiert ein Cycle-Start Paket. Auf dieses Paket folgen dann isochrone Pakete. Diese Pakete dürfen maximal 80% einer Runde einnehmen. Anschließend können asynchrone Pakete verschickt werden bis zum Beginn der nächsten Runde.

Zur Feherlerkennung verwendet Firewire einen 32 Bit CRC. Dieser Mechanismus kommt sowohl bei isochroner als auch bei asynchroner Datenübertragung zum Einsatz. Im asynchronen Übertragungsmodus kommen, zusätzlich zum CRC, Acknowledgementpakete zum Einsatz. Das heißt, der Sender erwartet für eine verschickte Nachricht eine Bestätigung vom Empfänger über deren Erhalt. Der isochrone Modus unterstützt dies nicht, da bei ihm ein vorhersagbares Zeitverhalten im Vordergrund steht.

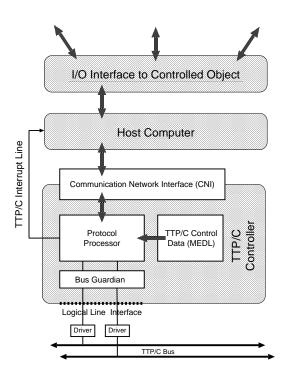

## 3.4.6 TTP/C

TTP/C [Kop97, AG02, TTP] ist ein Protokoll zur Echtzeitkommunikation zwischen elektronischen Komponenten von verteilten fehlertoleranten Systemen, die über einen Bus verbunden sind. Die einzelnen Knoten werden als Nodes bezeichnet. Ein Node (Abbildung 3.4) besteht aus einem TTP/C-Controller und einem Hostcomputer. Die Kommunikation zwischen Controller und Host findet über das Communication Network Interface (CNI) statt. Der Controller enthält einen Bus-Guardian, den Protokollprozessor und die TTP/C Message Descriptor List (MEDL).

Abbildung 3.4: Aufbau einer TTP/C Node, Quelle [AG02]

|      |         | Attribute |    |    |   |  |

|------|---------|-----------|----|----|---|--|

| Zeit | Adresse | D         | L  | -1 | Α |  |

| t1   | 0x0001  | Out       | 8  | Ι  | 0 |  |

| t2   | 0x00A1  | In        | 8  | Ν  | 0 |  |

| t3   | 0x003C  | Out       | 16 | Ν  | 0 |  |

Abbildung 3.5: Aufbau der TTP/C Message Descriptor List, Quelle [Kop97]

Der Bus-Guardian ist eine unabhängige Einheit, die den Bus vor Timingfehlern durch den Controller schützt. Der Bus besteht aus zwei identischen Kanälen. Beim Senden wird die Nachricht über jeden der Kanäle geschickt. Die MEDL ist eine statische Datenstruktur im TTP/C-Controller (Abbildung 3.5). Sie enthält den Zeitpunkt, wann eine Nachricht, deren Adresse im Adressfeld steht, gesendet oder empfangen werden muss. Die Adresse gibt an, wo die Nachricht im CNI steht. Die Attribute in der MEDL geben die Richtung (D - in/out), die Länge der Nachricht (L), die Art der Nachricht (I - Initialisierung / Normal) und zusätzliche Parameter (A) für Modus und Rollenwechsel an.

Abbildung 3.6: TTP/C Frameformat, Quelle [Kop97]

Der Frame (Abbildung 3.6), der gesendet wird, besteht aus einem Header, dem Nutzdatenfeld und einem 16 Bit CRC. Es gibt grundsätzlich zwei Nachrichtenarten. Initialisierungsnachrichten und normale Nachrichten. Bei Initialisierungsnachrichten wird der CRC über den Header und die Nutzdaten gebildet. Die CRC-Prüfsumme normaler Nachrichten setzt sich aber nicht nur aus dem Header und den Nutzdaten zusammen (Abbildung 3.7). Um eine Übereinstimmung der Controllerzustände zu bewirken, ohne dafür extra Nachrichten versenden zu müssen, bildet der Sender den CRC, zusätzlichen zu Header und Nutzdaten, auch aus dem aktuellen Controllerzustand (C-State). Der C-State enthält informationen über die aktuelle Zeit im Sender, die aktuelle Position in der MEDL, den aktuellen Modus, anstehende Moduswechsel und Zugehörigkeit. Zur Überprüfung der eingehenden Nach-

CRC-Berechnung beim Sender:

Header Datenfeld C-State des Sender CRC

Nachricht auf dem Bus:

Header Datenfeld CRC

CRC-Berechnung beim Empfänger:

Header Datenfeld C-State des Empfängers CRC

Abbildung 3.7: Berechnung des CRC bei TTP/C, Quelle [Kop97]

richt, bildet der Empfänger den CRC aus den empfangen Header und Nutzdaten und seinem eigenen C-State. Die Clock-Synchronisation findet auch ohne zusätzliche Nachrichten statt. Da der Zeitpunkt, zu dem ein Node eine bestimmt Nachricht sendet, Sender und Empfänger bekannt sind, wird darüber die Zeit synchron gehalten. Damit können Übertragungsfehler, Wiederholung, Verlust, Einfügungen, falsche Abfolge, zeitliche Verzögerung und Maskierung erkannt werden.

## $3.4.7 \quad TTP/A$

TTP/A ist eine eingeschränkte Version des TTP/C Protokolls. Es ist kein verteiltes sondern ein Multimasterprotokoll. Es wurde für günstige Feldbusanwendungen entwickelt. Zur Realisierung kann ein Standard-UART (Universal Asynchronous Receiver Transmitter) verwendet werden. Eine Nachricht besteht dort aus einem Startbit, 8 Bit Nutzdaten, einem Paritätsbit und einem Stopbit.

Bei TTPA/A gibt es zwei Nachrichtenarten, die Fireworks- und die Datennachricht. Zur Kennzeichnung dient bei Fireworksnachrichten ungerade Parität, bei Datennachrichten gerade Parität. Die Datenübertragung ist in Runden aufgeteilt. Jede Runde beginnt mit dem Senden einer Fireworksnachricht durch den aktiven Master. Die Nachricht enthält den Namen der aktiven Message Descriptor List (MEDL) für diese Runde. Außerdem dient sie zur globalen Synchronisation der Nodes. Anschließend folgt eine Sequenz von Datennachrichten, bis die aktive MEDL abgearbeitet ist. Danach kann eine neue Runde starten. Das Senden einer Nachricht muss zu einem vorbestimmten Zeitpunkt erfolgen und in einem bestimmten Zeitfenster abgeschlossen

sein. Diese Informationen müssen bei der Entwicklung der MEDL festgelegt werden.

Um einen UART für TTP/A einsetzen zu können, muss dieser gerade und ungerade Parität unterstützen. Gerade Parität dient zur Kennzeichnung und zur Fehlererkennung in Datennachrichten. Tritt ein Fehler in den Nutzdaten auf, bleiben die alten Daten erhalten und der Fehler wird innerhalb der Node dem Host mitgeteilt.

Zur Erkennung von Fehlern im zeitlichen Ablauf, dient die MEDL. Die Sequenz von Sende und Empfangsvorgängen ist in der MEDL festgelegt und wird von allen Nodes beobachtet. Wird ein RDI (receive data interrupt, Daten wurden empfangen) außerhalb des zulässigen Zeitfensters ausgelöst, liegt ein Kontrollfehler vor. Bleibt eine im Zeitfenster erwartete Nachricht aus, dann werden die alten Daten nicht verändert und der Fehler zum Host gemeldet. Beim Auftreten eines Kontrollfehlers in einer Node, beendet diese für sich die aktuelle Runde. Die Node wartet dann auf die nächste Fireworksnachricht. Sendet der aktive Master nicht innerhalb eines bestimmten Timeouts, dann wird ein Reservemaster aktiviert.

Mit den Fehlererkennungsmechanismen lassen sich Nachrichtenwiederholung, Verlust, falsche Abfolge, zeitliche Verzögerung und Maskierung erkennen. Auch fehlerhafte Daten, bei denen eine ungerade Anzahl von Bits verfälscht ist, lassen sich erkennen. Mehr Informationen zum TTP/A Protokoll beinthalten [Kop97], [AG01] und [TTP].

#### 3.4.8 LVDS

LVDS (Low Voltage Differential Signaling) ist eine Technologie die im IEEE Standard 1596.3 definiert ist. Sie erlaubt es, Signale mit einem geringen Spannungsunterschied (250 . . . 400 mV) zwischen Low und High-Pegel zu übertragen. Durch den geringen Spannungshub sind hohe Datenübertragugsraten bei geringem Leistungsverbrauch möglich. Die Spezifikation [Sem00, LVD] umfaßt nur die Definition der elektrischen Eigenschaften auf Bitübertragungsebene. Ein festes Protokoll zur Datenübertragung wird, wie bei RS-485, nicht definiert.

In den meisten LVDS Empfängern sind interne Failsafe-Schaltungen eingebaut. Sie zwingen den Ausgang unter gewissen Fehlerbedingungen in einen bekannten logischen Pegel, so dass keine undefinierten Ausgangsspannungen auftreten. Diese Failsafe-Mechanismen treten bei offenen Eingangspins, unterbrochenen Eingängen und unzureichender Energiezufuhr in Kraft.

#### 3.4.9 Controller Area Network (CAN)

Das Controller Area Network (CAN) bezeichnet einen seriellen Bus, mit einer Datenübertragungsrate von 1 Mbit/s bei maximal Leitungslänge von 40 m. Größere Distanzen erfordern geringere Übertragunsraten. Bei der Datenübertragung findet keine Adressierung statt. Jeder Knoten am Bus kann anhand eines Identifiers, der in einer Message Descriptor List szeht, entscheiden, ob er die Nachricht annimmt oder nicht. Bei CAN 1.0 können pro Nachricht 8 Byte Nutzdaten verschickt werden. Der Identifier ist 11 Bit lang. Es gibt 4 Arten von Paketen, die beim CAN Frame genannt werden. Es sind der Daten-, Remote-, Error- und Overload-Frame. Die CAN 2.0-Spezifikation verwendet einen 29 Bit langen Identifier. Damit ist eine größere Anzahl Geräte ansprechbar. Außerdem wurde die Nutzlast der Datenpakete auf bis zu 64 Byte erhöht.

Die Fehlererkennungsmechanismen sind bei beiden Spezifikationen gleich. Das CAN benutzt zur Fehlererkennung CRC16. Dabei wird aus dem Start-, Arbitration-, Control- und Datenfeld die Prüfsumme gebildet. Das Generatorpolynom lautet  $G(x) = x^{15} + x^{14} + x^{10} + x^8 + x^7 + x^4 + x^3 + 1$ . Der

Abbildung 3.8: Datenrahmen für CAN 1.0 und 2.0, Quelle [Dem93]

Sender überträgt im ACK-Bit ein High. Stellt ein Empfänger eine Übereinstimmung mit der CRC-Sequenz fest, überschreibt er das Bit mit Low. In diesem Fall erfolgte die Übertragung ohne Fehler. Falls die Übertragungs nicht fehlerfrei verlief, dann sendet ein Busteilnehmer ein Error-Frame. Es wird von den anderen Einheiten erkannt, worauf diese die letzten empfangenen Daten verwerfen. Die Busteilnehmer besitzen je zwei Zähler. Dabei ist einer für das Senden und einer für das Empfangen zuständig. Mit diesen Zählern ist es möglich defekte Busteilnehmer zu erkennen. Bei einem Fehler wird der Zähler um eins erhöht, bei einer erfolgreichen Übertragungs dagegen wieder um eins verringert. Übersteigt ein Zähler den Wert von 128 dann wird der entsprechende Busteilnehmer in den "Error passiv "Staus gebracht. Dadurch ist es ihm nur noch möglich zu senden und empfangen, wenn kein anderer Busteilnehmer den Bus benutzt. Treten weitere Fehler auf, schaltet sich der Knoten bei einem Zählerstand von 256 vom Bus ab. Weiterführende Informationen zu diesem Standard stehen in [CANa], [CANb] und [Dem93].

#### 3.4.10 Ethernet

Ethernet [Hei95, San] ist ein weit verbreitetes Netzwerkprotkoll. Sein Einsatzspektrum reicht von der Verbindung zweier PC's bis hin zum Aufbau komplexer Netzwerksysteme. Dabei können als Übertragungsmedium für die Daten Kabel, Glasfaserkabel oder Funk eingesetzt werden. Die Topologie kann als Token Ring oder als Bus, an dem mehrere Geräte angeschlossen sind, aufgebaut sein.

Ethernet verwendet zum Zugriff auf das Übertragungsmedium das CSMA/CD Zugriffsverfahren (Carrier Sense Multiple Access/Collision Detection). Vor dem Senden prüft die Station ob schon eine Nachricht einer anderen Station auf dem Bus liegt. Ist das nicht der Fall dann legt sie ihre Nachricht auf den Bus. Haben allerdings mehrere Stationen gleichzeitig geprüft und versuchen gleichzeitig Daten auf den Bus zu legen, dann kommt es zu einer Kollision. Diese muss von den einzelnen Stationen erkannt werden. Daraufhin ziehen die Stationen ihre Signale zurück und versuchen es zeitversetzt mit einem Fairnessintervall noch einmal.

Zur Fehlererkennung benutzt der Ethernet-Standard den Cyclic Redundancy Check. Dabei wird CRC32 mit dem Generatorpolynom  $G(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$  eingesetzt. Das Erzeugen sowie das Auswerten des CRC-Wertes erfolgt in der Sicherungsschicht.

# 3.5 Integration von Fail-safe-Verhalten in Schnittstellen

Systeme mit harten oder weichen Echtzeitbedingungen verlangen ein vorhersagbares Systemverhalten. Die gilt sowohl für den fehlerfreien Betrieb, als auch für den Betrieb im Fehlerfall. Um dies zu erreichen wird Fail-safe-Verhalten eingesetzt.

Bisher wurde Fail-safe-Verhalten in die Systeme direkt integriert. Der hier vorgestellte Ansatz besteht darin, diesen Mechanismus schon in die verbindende Schnittstelle zweier Systeme einzubinden. Ein großer Vorteil dieses Ansatzes ist, dass an den Systemen selbst keine Änderungen vorgenommen werden müssen. Der Einsatz von verschiedenen Intellectual Properties (IP) wird somit vereinfacht. Der Entwurf von Systemen aus IP's beschränkt sich somit auf die Entwicklung der Schnittstellen zwischen den Systemen. Änderungen an den Komponenten selbst sind dadurch nicht notwendig. Um gegen eventuell auftetende Fehler bei der Kommunikation gewappnet zu sein, wird Fail-safe-Verhalten in die Schnittstelle integriert.

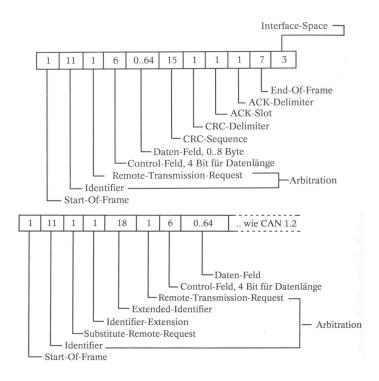

Abbildung 3.9: Aufgaben zur Erfüllung von Fail-safe-Verhalten in Schnittstellen

Zur Realisierung von Fail-safe-Verhalten sind allgemein drei Aufgaben (Abbildung 3.9) zu erfüllen. Das sind die Fehlererkennung, die Generierung von Fail-safe-Daten und die Überwachung und Kontrolle der Erkennung und Generierung.

Die Aufgabe der Fehlererkennung realisiert der **Protokollguard**. Durch ihn werden Mechanismen zur Fehlererkennung, wie sie in Abschnitt 3.3 vorgestellt wurden, in die Schnittstelle integriert. Der Protokollguard überprüft das eingehende Protokoll auf Korrektheit. Dabei ist die Art der Fehlererkennung abhängig vom Protokoll, das empfangen wird, wie Abschnitt 3.4 gezeigt

hat. Im Fehlerfall generiert der Protokollguard ein Fehlersignal, das von einer Kontrolleinheit interpretiert werden kann. Es ist durchaus vorstellbar, dass der Protokollguard verschiedene Fehlersituationen erkennen kann und für jede Fehlersituation ein individuelles Fehlersignal erzeugt. Somit kann die Kontrolleinheit auf unterschiedliche Fehlersituationen angemessen reagieren.

Der Generator für die Fail-safe-Daten erzeugt im Fehlerfall Daten, um ein System in einen fehlersicheren Zustand zu bringen. Um Fail-safe-Daten für ein System erzeugen zu können, muss man wissen, durch welche Daten ein System in einen fehlersicheren Zustand gebracht werden kann. Es ist also Wissen über das angesteuerte System notwendig. Dieses Wissen wird in den Generator bei der Entwicklung der Schnittstelle mit eingebunden. Der Generator ist in der Lage eine festgelegte Datensequenz zu erzeugen oder auch eine komplexe Steuerung zu realisieren. Dadurch ist es möglich Failsafe-Datengeneratoren für ein breites Anwendungsspektrum einzusetzen.

Zur Überwachung und Kontrolle der Erkennung und Generierung dient eine Kontrolleinheit. Sie hat die Aufgabe, die Fehlersignale auszuwerten und entsprechende Maßnahmen zu treffen. Die Maßnahme besteht darin, einen Generator für Fail-safe-Daten zu aktivieren. Dabei kann die Kontrolleinheit durchaus auf mehr als einen Generator zurückgreifen. Dies ermöglicht eine individuelle Reaktion auf Fehlersituationen. Die Einbindung der Kontrolleinheit in das Fail-safe-Verhalten bringt den Vorteil mit sich, dass der Protokollguard und der Fail-safe-Datengenerator unabhängig voneinander entwickelt werden können und zwei eigenständige Komponenten bilden.

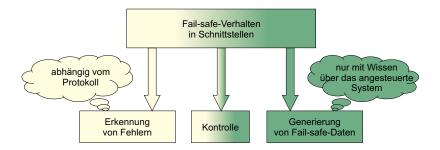

Ein Interfaceblock, wie er in Kapitel 2.1 vorgestellt wurde, erfüllt alle Voraussetzungen zur Integration von Fail-safe-Verhalten in Schnittstellen. Im Modell des Interfaceblocks gibt es vier Komponenten. Die Kontrolleinheit, zwei Protokollhandler, wobei einer zum Empfangen und einer zum Senden benötigt wird (im folgenden als  $PH_{in}$  und  $PH_{out}$  bezeichnet) und den Sequenzhandler. Im Folgenden wird beschrieben, wie sich die bisherigen Konzepte in den Interfaceblock integrieren lassen. Zur Veranschaulichung zeigt Abbildung 3.10 ein mögliches Fail-safe-Verhalten in einem Interfaceblock.

Die Feherlerkennung sollte so nah wie möglich an der Datenquelle sitzen, damit die Verzögerungszeiten zwischen dem Auftreten eines Fehlers und dessen Erkennung so gering wie möglich sind. Aus diesem Grund bewerkstelligt die Fehlererkennung der aktive Modus des  $PH_{in}$ . Innerhalb des Interfaceblocks ist er der Erste, der die Daten erhält. Außerdem ist in diesem Modus der Kommunikationsautomat zur Erkennung das aktuell empfangenen Protokolls implementiert, der zum Empfangen von Daten nötig ist. Ein weiterer

Abbildung 3.10: Fail-safe-Verhalten in einem Interfaceblock

Vorteil ist, dass man die Erkennung von Übertragungsfehlern parallel zum Datenempfang stattfinden lassen kann, wenn man die Fehlererkennung in den Modus implementiert. Dabei kann man auf die protokollspezifischen Fehlererkennungsmechanismen der Protokolle (Abschnitt 3.4) zurückgreifen. Es ist aber zu beachten, dass beim Auftreten eines Fehlers die Daten nicht an den Sequenzhandler weitergereicht werden und ein Statussignal für die Kontrolleinheit generiert wird, dass diese über den Fehler informiert.

Zur Erkennung von Zeitüberschreitungsfehlern ist ein Timer notwendig. Dabei gibt es zwei verschiedene Implementierungsvarianten. Falls das eingehende Protokoll schon Echtzeitanforderungen unterliegt, ist es sinnvoll den Timer in den Modus zu integrieren. Damit ist man bezüglich verschiedener Protokolle flexibel, die unterschiedlichen Echtzeitanforderungen unterliegen. Wenn der Interfaceblock allerdings zur Umwandlung eines ereignisgesteuerten (event-triggered) Protokolls in ein zeitgesteuertes (time-triggered) benutzt wird, muß der Timer in die Kontrolleinheit integriert werden. Zusätz-

lich muss der Modus im  $PH_{in}$  ein Statussignal generieren für den Fall, dass er Daten empfangen hat. Liegt der Zeitpunkt innerhalb der vorgeschriebenen Zeit, dann können die Daten normal weitergegeben werden. Wurde allerdings das Ende des Timers erreicht und sind keine neuen Daten eingegangen, dann muss der Fail-safe-Datengenerator aktiviert werden, um Daten für den nächsten Sendezyklus zu generieren.

Der Generator der Fail-safe-Daten wird als Modus des Sequenzhandlers implementiert. Bei der Implementierung ist ein genaues Wissen über die Komponente notwendig, für die die Fail-safe-Daten generiert werden sollen. Zum Beispiel ein reines Weiterschicken von alten Daten könnte zu unbeabsichtigten Ergebnissen führen. Das wäre unter anderem der Fall, wenn relative Positionierungsdaten für einen Roboter gesendet werden. Die alten Daten enthalten Differenzwerte zur aktuellen Position. Werden diese geschickt, würde sich der Roboter weiterbewegen, was vom Anwender aber nicht beabsichtigt ist. Deshalb muss der Fail-safe-Datengenerator in solch einem Fall einen Nullvektor erzeugen. Aus diesem Grund ist vor dem Einsatz von Fail-safe-Verhalten zu untersuchen, welche Daten eine Komponente in einen sicheren Zustand bringen und dieses Wissen in den Modus zu implementieren. Im Interfaceblock ist es auch möglich, auf unterschiedliche Fehler mit verschiedenem Fail-safe-Verhalten zu reagieren. Wenn die Fehlererkennung mehrere Fehler unterscheiden kann oder es mehrere Fehlerquellen gibt, kann für jede Fehlersituation ein anderer Modus für den Sequenzhandler implementiert werden. Je nach Fehlersituation wird der entsprechende Modus aktiviert.

Zur Kontrolle und Uberwachung der Fehlererkennung und der Generierung von Fail-safe-Daten ist die Kontrolleinheit zuständig. In ihr laufen alle Statusleitungen der Handler und ihrer Modi zusammen. Wenn sie vom Protokollguard eines  $PH_{in}$ -Modus einen Fehler gemeldet bekommt, dann kann sie sofort reagieren und im Sequenzhandler den entsprechenden Fail-safe-Modus aktivieren. Wenn dann in einem weiteren Durchlauf des  $PH_{in}$ -Modus kein Fehler mehr festgestellt wird, dann schaltet die Kontrolleinheit den Sequenzhandler wieder auf Normalbetrieb.

Der Einsatz von Fail-safe-Verhalten in einem IFB ist auch bei dynamisch rekonfigurierbaren FPGA's denkbar, bei denen in der Rekonfigurationsphase das FPGA nicht angehalten wird. Dazu muss die Kontrolleinheit über den Beginn der Rekonfigurationsphase informiert werden. Sie aktiviert dann einen Fail-safe-Modus für die Dauer der Rekonfiguration. Nach dem Abschluss der Phase schaltet die Kontrolleinheit den IFB wieder auf Normalbetrieb bzw. in einen Sequenzhandlermodus der der neuen Konfiguration entspricht.

Das Einsatzfeld von Fail-safe-Verhalten in einem Interfaceblock ist groß. Es reicht von einfachen Kommunikationsaufgaben über die Umwandlung von ereignisgesteuerten in zeitgesteuerte Signale für Echtzeitanforderungen bis hin zu komplexen Systemen, die während des Betriebs an neue Funktionen angepasst werden können. Der IFB bietet dabei eine gute Grundlage, um unterschiedlichsten Anforderungen gerecht zu werden.

# 4 Demonstrator

In diesem Kapitel wird ein Demonstrator vorgestellt, an dem die Konzepte, die in dieser Arbeit vorgestellt wurden, umgesetzt werden. Zunächst erfolgt eine kurze Betrachtung über den Nutzen eines Demonstrators. Anschließend wird dessen Aufbau und Funktionsweise erläutert. Zum Schluss werden die Konzepte zur Implementierung beschrieben und umgesetzt.

# 4.1 Bedeutung

Ein Demonstrator bietet den Vorteil, erarbeitete theoretische Konzepte im praktischen Einsatz zu erproben und zu validieren. Dadurch können Schwachstellen und Fehler im theoretischen Modell aufgedeckt und korrigiert werden. Außerdem kann die Praxisrelevanz der Konzepte gezeigt werden. Liegt nur ein theoretisches Modell vor, so kann es durchaus sein, dass es sich nicht oder nur schwer in die Praxis umsetzen lässt und damit nie zum Einsatz kommen kann. Umgekehrt kann eine rein praktische Implementierung eventuell nicht allgemein modelliert werden und ist damit auf ein spezielles Anwendungsgebiet beschränkt. Deshalb werden für den Demonstrator zunächst die Modellierungsansätze vorgestellt, bevor die Implementierung erfolgt.

#### 4.2 Aufbau und Funktionsweise

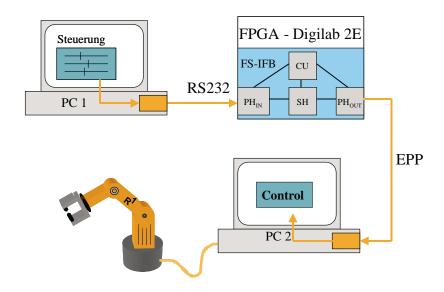

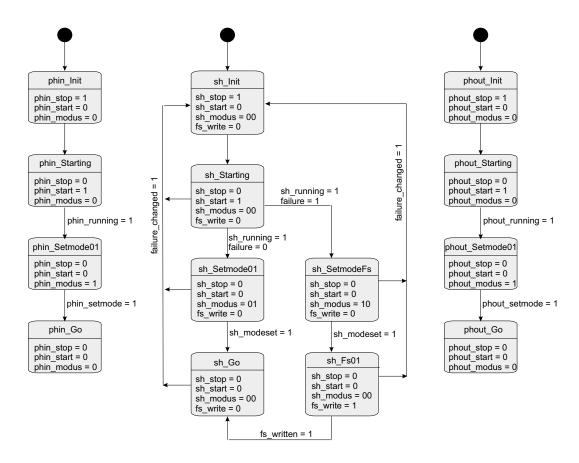

Der Demonstrator (Abbildung 4.1) ist aus zwei PC's, einem Roboterarm und einem Digilab 2E FPGA Board mit einem Xilinx Spartan 2E XC2S200E FPGA [Inc02] aufgebaut. Die Verbindung zwischen PC1 und FPGA-Board wird über die serielle Schnittstelle hergestellt. Die Verbindung von FPGA-Board und PC2 geschieht über die parallel Schnittstelle.